In qualità di fornitore di semiconduttori più venduto al mondo, Intel non solo sviluppa chip, ma ne ricerca anche le tecnologie di base. La Component Research Division di Intel presenta otto progetti all’International Meeting on Electronic Devices (IEDM 2021), che vanno dai transistor CMOS in miniatura ai processi di stacking 3D e ai chip per computer quantistici.

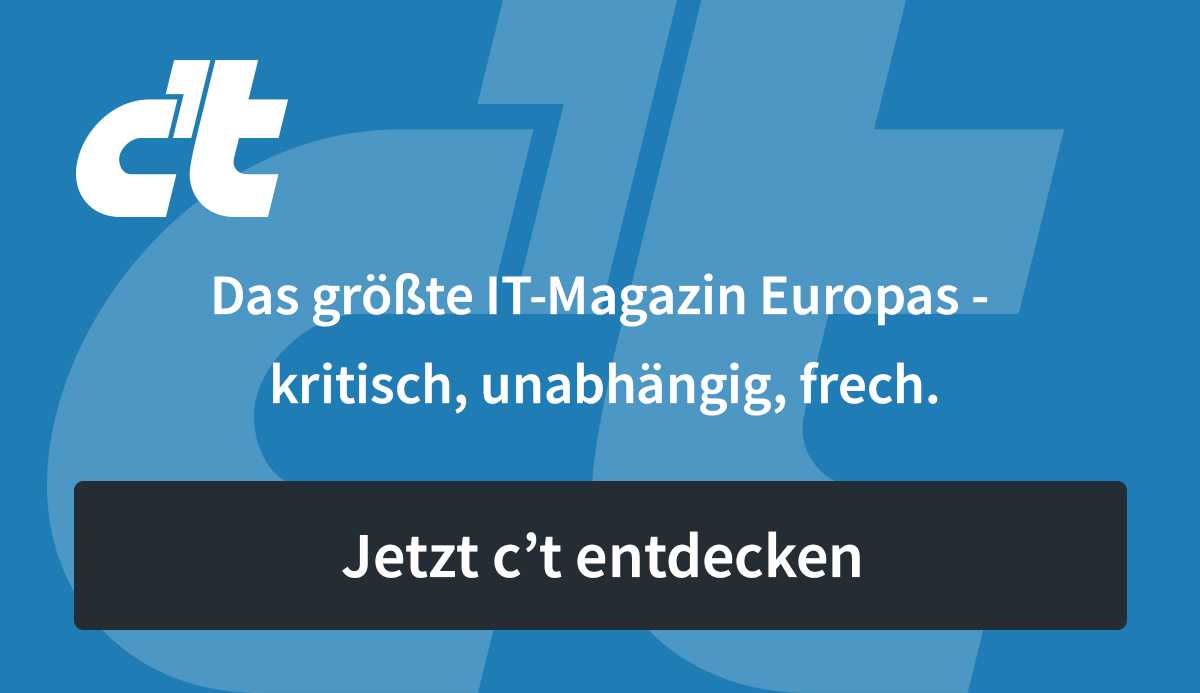

In Foverros Direct alias HBI, Intel entra in contatto diretto con due stampi in silicio impilati con piccole punte di rame.

(Foto: Intel)

Interconnessione di collegamento ibrida (HBI)

Mentre le nuove strutture a transistor come il FETT complementare (CFET) e il gate 3D all around (GAA) appariranno nella produzione in serie solo dopo il 2025 e gli elementi logici di spin-orbita magnetica (MESO) anche più tardi, “Foveros Direct” di Intel noto anche come The Il nome Hybrid Bonding Interconnect (HBI) è praticamente davanti alla porta. Secondo Intel, può essere utilizzato dalla tecnologia di produzione a 7 nm “Intel 4” o “Intel 3”.

Alla HBI, Intel imballa due chip di silicio direttamente uno sopra l’altro, con poco rame a contatto l’uno con l’altro. Secondo Intel, ciò significa che è possibile aumentare significativamente il numero di contatti per millimetro quadrato rispetto ai precedenti die-stack che utilizzavano piccole sfere di saldatura (bave). AMD ha già annunciato che otterrà “3D V-Cache” dai prossimi processori Epyc e Ryzen di TSMC utilizzando un processo simile. Xperi ne concede in licenza uno anche attraverso la sua divisione Tessera “Direct Bond Interconnect” (DBI) o ZiBond.

GAA-FET-Stapel

Non solo Intel, ma anche Samsung e TSMC sostituiranno il transistor ad effetto di campo (FET) con un elettrodo di gate a forma di aletta (FinFET) che è stato costruito per diversi anni con i prossimi cicli di produzione. Vengono invece utilizzati FET nanoribbon, nanosheet e universal gate (GAA). La versione Intel si chiama RibbonFET e dovrebbe arrivare dopo il 2023 con tecnologia di produzione “Intel 20A”.

Nel processo di fabbricazione di semiconduttori a ossido di metallo complementare (CMOS) vecchio di decenni, si combina un MOSFET a canale n e un MOSFET a canale p (NMOS/PMOS), solitamente in tandem.

Tuttavia, per risparmiare spazio, ovvero per posizionare più transistor sulla superficie del chip, Intel prevede di impilarli in futuro. Per “Nanoribbon 3D Stacking”, Intel Component Research sta sperimentando due approcci: costruire due strati funzionali uno per uno (in sequenza) con uno strato isolante di ossido di silicio tra di loro o una struttura “autoallineante” direttamente uno sopra l’altro . Strutture simili sono anche chiamate FET complementari (CFET).

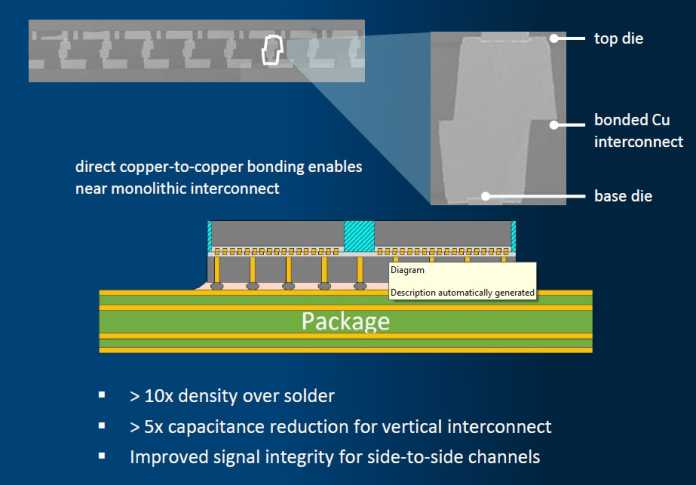

La logica MESO (a sinistra) potrebbe eventualmente sostituire il CMOS; STMG utilizza limiti di campo magnetico in movimento.

(Foto: Intel)

MESO .logica

Quando non tutti gli stack CMOS aiutano a mantenere la legge di Moore, è il momento di sostituire il CMOS. Ecco perché da anni si tengono conferenze sui nanotubi di carbonio (CNT) alle conferenze sui semiconduttori.

Intel ora riferisce di primi esperimenti di successo con elementi logici MESO a temperatura ambiente, ma scrive che “possono essere prodotti in serie”.

Un’altra idea sono i componenti di coppia che utilizzano la trasmissione di confine del campo magnetico (pareti di dominio, DW); Intel sta collaborando con l’IMEC europeo alla ricerca sullo Spin Torque Majority Gate (STMG), che è una combinazione di un componente logico e di memoria.

Intel Viram

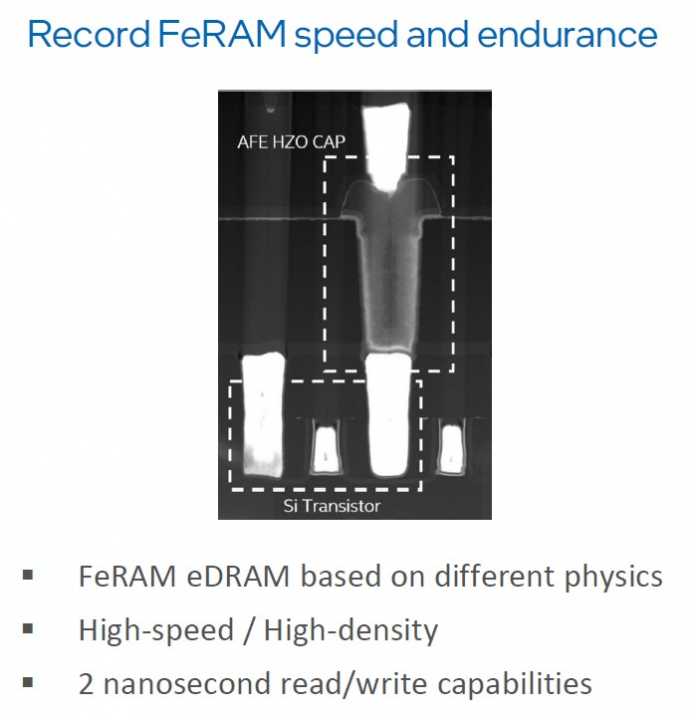

Cella Viram con ossido di afnio

(Foto: Intel)

Una cella di memoria FeRAM che utilizza un condensatore antielettrolitico a base di afnio invece di un’architettura di condensatore convenzionale potrebbe essere più vicina all’uso pratico. Secondo Intel, ciò significa che ha misurato tempi di latenza molto brevi di 2 nanosecondi e una resistenza di scrittura (resistenza) molto elevata nell’intervallo di 1 miliardo di cicli. Tuttavia, anche altri produttori stanno lavorando su FeRAM, tra cui FMC a Dresda.

Altre innovazioni che Intel introdurrà all’IEDM 2021 includono l’integrazione di transistor di commutazione al nitruro di gallio (GaN) ad alte prestazioni su chip CMOS da 300 mm. Ciò significa che trasformatori di tensione efficienti possono essere integrati direttamente nei futuri processori.

Inoltre, Intel sta sperimentando composti di calcogeno di metalli di transizione (monostrati TMD) come il disolfuro di molibdeno (MoS).2) come sostituto del silicio in alcuni punti nei semiconduttori. Questo può rendere alcune strutture più piccole.

(una linea)

“Esperto di birra per tutta la vita. Appassionato di viaggi in generale. Appassionato di social media. Esperto di zombi. Comunicatore.”